# Si7050/1/3/4/5-A20/1

## I<sup>2</sup>C TEMPERATURE SENSORS

#### Features

- High Accuracy Temperature Sensors

- Si7051: ±0.1 °C (max)

- Si7053: ±0.3 °C (max)

- Si7054: ±0.4 °C (max)

- Si7055: ±0.5 °C (max)

- Si7050: ±1.0 °C (max)

- Wide operating voltage (1.9 to 3.6 V)

- -40 to +125 °C operating range

#### Applications

- HVAC/R

- Thermostats

- White goods

- Computer equipment

- Portable consumer devices

- Accuracy maintained over the entire operating temperature and voltage range

- Low Power Consumption

- 195 nA average current @ 1 Hz sample rate

- 14-bit resolution

- Factory calibrated

Asset tracking

Cold chain storage

Battery protection

Industrial controls

Medical equipment

- I<sup>2</sup>C interface

- 3x3 mm DFN package

The Si705x Digital Temperature Sensors offer industry-leading low power consumption and high accuracy across the entire operating voltage and temperature range. These monolithic CMOS ICs feature a band-gap temperature sensor element, an analog-to-digital converter with up to 14-bit resolution, signal processing, calibration data, and an I<sup>2</sup>C interface. The patented use of novel signal processing and analog design enables the sensors to maintain their accuracy over a wide temperature and voltage range, while consuming very little current.

The temperature sensors are factory-calibrated and the calibration data is stored in the on-chip non-volatile memory. This ensures that the sensors are fully interchangeable, with no recalibration or software changes required.

The Si705x devices are available in a 3x3 mm DFN package, and the industry-standard I<sup>2</sup>C interface can operate at up to 400 kHz. Requiring just 195 nA of average current when sampled once per second, the Si705x can operate for several years with just a single coin cell battery.

The Si705x devices offer an accurate, low-power, factory-calibrated digital solution ideal for measuring temperature in applications ranging from HVAC/R and asset tracking to industrial and consumer platforms.

Sonions

## Si7050/1/3/4/5-A20/1

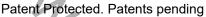

#### **Functional Block Diagram**

## TABLE OF CONTENTS

### <u>Section</u>

### <u>Page</u>

| 1. Electrical Specifications                                                          |      |

|---------------------------------------------------------------------------------------|------|

| 2. Typical Application Circuits                                                       |      |

| 3. Bill of Materials                                                                  |      |

| 4. Functional Description                                                             |      |

| 5. I2C Interface                                                                      |      |

| 5.1. Issuing a Measurement Command                                                    | .13  |

| 5.2. Reading and Writing User Registers                                               | . 14 |

| 5.3. Electronic Serial Number                                                         | .15  |

| 5.4. Firmware Revision                                                                | .16  |

| 6. Control Registers                                                                  | .17  |

| 6.1. Register Descriptions                                                            |      |

| 7. Pin Descriptions: Si705x (Top View)                                                |      |

|                                                                                       |      |

| 8. Ordering Guide                                                                     | .20  |

| 9.1. Package Outline: 3x3 6-Pin DFN                                                   | .20  |

| 10. PCB Land Pattern and Solder Mask Design                                           |      |

| 11. Top Marking                                                                       | .22  |

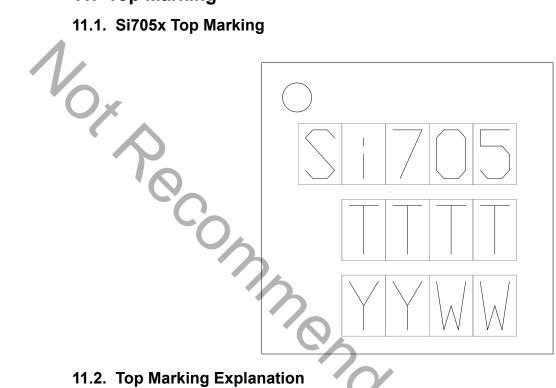

| <b>11. Top Marking</b> 11.1. Si705x Top Marking         11.2. Top Marking Explanation | .22  |

| 11.2. Top Marking Explanation                                                         | .22  |

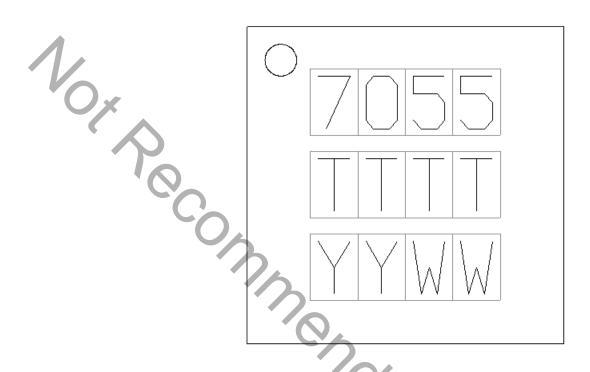

| 11.3. Si7055-A20-ZM (Matte Tin Finish Lead Frame) Top Marking                         | .23  |

| 11.4. Si7055-A20-ZM (Matte Tin Finish Lead Frame) Top Marking Explanation             |      |

| 12. Additional Reference Resources                                                    |      |

| Decument Change List                                                                  | .25  |

|                                                                                       |      |

|                                                                                       |      |

### 1. Electrical Specifications

Unless otherwise specified, all min/max specifications apply over the recommended operating conditions.

#### **Table 1. Recommended Operating Conditions**

| Parameter             | Symbol | Test Condition | Min | Тур | Max  | Unit |

|-----------------------|--------|----------------|-----|-----|------|------|

| Power Supply          | Vdd    |                | 1.9 | _   | 3.6  | V    |

| Operating Temperature | TA     |                | -40 | —   | +125 | °C   |

#### **Table 2. General Specifications**

$1.9 \le VDD \le 3.6$  V; TA = -40 to 125 °C default conversion time unless otherwise noted.

| Parameter           | Symbol            | Test Condition                                                        | Min       | Тур       | Max       | Unit |

|---------------------|-------------------|-----------------------------------------------------------------------|-----------|-----------|-----------|------|

| Input Voltage High  | VIH               | SCL, SDA pins                                                         | 0.7 x Vdd |           | —         | V    |

| Input Voltage Low   | VIL               | SCL, SDA pins                                                         | —         |           | 0.3 x Vdd | V    |

| Input Voltage Range | Vin               | SCL, SDA pins with respect to GND                                     | 0.0       | _         | Vdd       | V    |

| Input Leakage       | lı∟               | SCL, SDA pins                                                         | _         |           | 1         | μA   |

| Output Voltage Low  | Vol               | SDA pin; IoL = 2.5 mA; VDD = 3.3 V                                    | _         |           | 0.6       | V    |

|                     |                   | SDA pin; IoL = 1.2 mA;<br>VDD = 1.9 V                                 |           | _         | 0.4       | V    |

| Current             | IDD               | Temperature conversion in progress                                    | _         | 90        | 120       | μA   |

| Consumption         |                   | Standby, –40 to +85 °C <sup>1</sup>                                   | —         | 0.06      | 0.62      | μA   |

|                     |                   | Standby, –40 to +125 °C <sup>1</sup>                                  | —         | 0.06      | 3.8       | μA   |

|                     |                   | Peak IDD during powerup <sup>2</sup>                                  | _         | 3.5       | 4.0       | mA   |

|                     |                   | Peak IDD during I <sup>2</sup> C operations <sup>3</sup>              | _         | 3.5       | 4.0       | mA   |

| Conversion Time     | t <sub>CONV</sub> | 14-bit temperature                                                    | -         | 7         | 10.8      | ms   |

|                     |                   | 13-bit temperature                                                    |           | 4         | 6.2       | ms   |

|                     |                   | 12-bit temperature                                                    | 40        | 2.4       | 3.8       | ms   |

|                     |                   | 11-bit temperature                                                    |           | 1.5       | 2.4       | ms   |

| Powerup Time        | t <sub>PU</sub>   | From VDD ≥ 1.9 V to ready for a<br>conversion, 25 °C                  | _ 4       | 18        | 25        |      |

|                     | -                 | From VDD ≥ 1.9 V to ready for a<br>conversion, full temperature range | _         | $\langle$ | 80        | ms   |

|                     |                   | After issuing a software reset command                                | _         | 5         | 15        | •    |

Notes:

**1.** No conversion or  $I^2C$  transaction in progress. Typical values measured at 25 °C.

2. Occurs once during powerup. Duration is <5 msec.

3. Occurs during I<sup>2</sup>C commands for Reset, Read/Write User Registers, Read EID, and Read Firmware Version. Duration

is <100 μs when I<sup>2</sup>C clock speed is >100 kHz (>200 kHz for 2-byte commands).

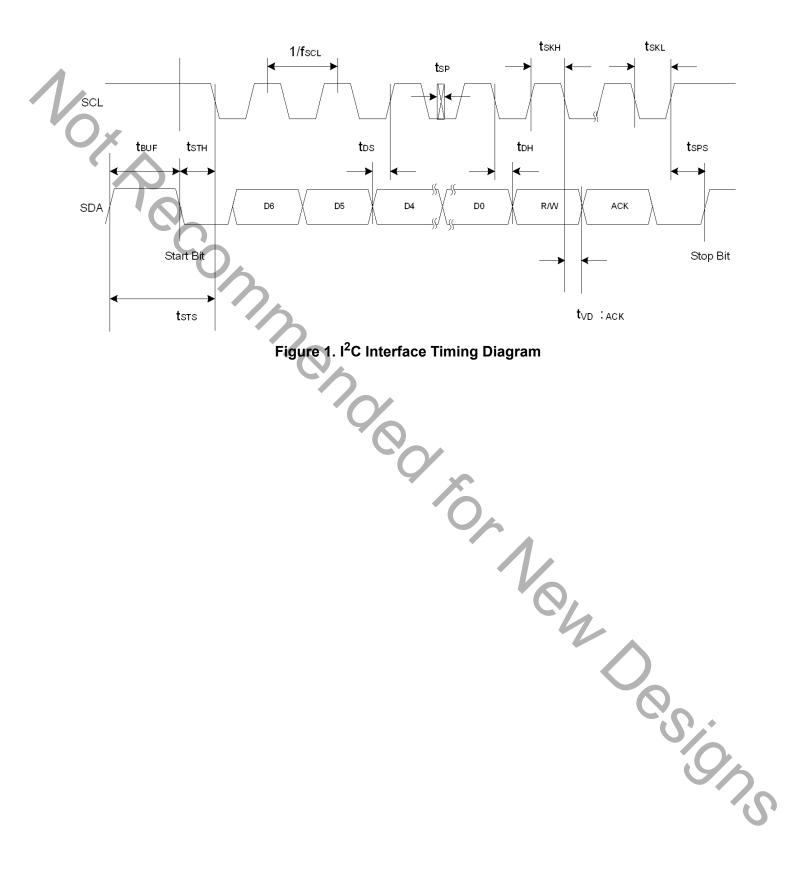

Table 3. I<sup>2</sup>C Interface Specifications<sup>1</sup>  $1.9 \le V_{DD} \le 3.6$  V;  $T_A = -40$  to +125 °C unless otherwise noted.

| Parameter                           | Symbol              | Test Condition                                | Min                    | Тур | Max | Unit |

|-------------------------------------|---------------------|-----------------------------------------------|------------------------|-----|-----|------|

| Hysteresis                          | V <sub>HYS</sub>    | High-to-low versus low-to-<br>high transition | 0.05 x V <sub>DD</sub> | —   | _   | V    |

| SCLK Frequency <sup>2</sup>         | f <sub>SCL</sub>    |                                               | _                      | _   | 400 | kHz  |

| SCL High Time                       | t <sub>SKH</sub>    |                                               | 0.6                    |     | _   | μs   |

| SCL Low Time                        | t <sub>SKL</sub>    |                                               | 1.3                    | —   |     | μs   |

| Start Hold Time                     | t <sub>STH</sub>    |                                               | 0.6                    | —   |     | μs   |

| Start Setup Time                    | t <sub>STS</sub>    |                                               | 0.6                    | —   |     | μs   |

| Stop Setup Time                     | t <sub>SPS</sub>    |                                               | 0.6                    | —   |     | μs   |

| Bus Free Time                       | t <sub>BUF</sub>    | Between Stop and Start                        | 1.3                    | —   |     | μs   |

| SDA Setup Time                      | t <sub>DS</sub>     |                                               | 100                    |     | _   | ns   |

| SDA Hold Time                       | t <sub>DH</sub>     |                                               | 100                    | —   |     | ns   |

| SDA Valid Time                      | t <sub>VD;DAT</sub> | From SCL low to data valid                    | _                      | _   | 0.9 | μs   |

| SDA Acknowledge Valid Time          | t <sub>VD;ACK</sub> | From SCL low to data valid                    | _                      |     | 0.9 | μs   |

| Suppressed Pulse Width <sup>3</sup> | t <sub>SPS</sub>    | 40                                            | 50                     |     |     | ns   |

#### Notes:

l

1. All values are referenced to  $V_{\text{IL}}$  and/or  $V_{\text{IH}}.$

2. Depending on the conversion command, the Si705x may hold the master during the conversion (clock stretch). At above 100 kHz SCL, the Si705x may also hold the master briefly for user register and device ID transactions. At the highest I<sup>2</sup>C speed of 400 kHz the stretching will be <10  $\mu$ s.

3. Pulses up to and including 50 ns will be suppressed.

## Si7050/1/3/4/5-A20/1

#### Table 4. Temperature Sensor

$1.9 \le V_{DD} \le 3.6 \text{ V}$ ; TA = -40 to +125 °C default conversion time unless otherwise noted.

| Parameter                  | Symbol           | Test Condition    | Min | Тур   | Мах               | Unit    |

|----------------------------|------------------|-------------------|-----|-------|-------------------|---------|

| Operating Range            |                  |                   | -40 |       | +125              | °C      |

| Accuracy <sup>1</sup>      |                  | Si7051            |     |       | ±0.1 <sup>2</sup> | °C      |

|                            |                  | Si7053            | _   | ±0.2  | ±0.3              | °C      |

|                            |                  | Si7054            |     | ±0.3  | ±0.4              | °C      |

| 0                          |                  | Si7055            |     | ±0.4  | ±0.5              | °C      |

|                            |                  | Si7050            |     | ±0.5  | ±1.0              | °C      |

| Repeatability/Noise        |                  | 14-bit resolution |     | 0.01  |                   |         |

|                            | 5                | 13-bit resolution |     | 0.02  |                   | °C RMS  |

| •                          |                  | 12-bit resolution |     | 0.04  |                   | C RIVIS |

|                            | 1                | 11-bit resolution |     | 0.08  |                   |         |

| Response Time <sup>3</sup> | т <sub>63%</sub> | Unmounted device  | _   | 0.7   |                   | S       |

|                            |                  | Si705x-EB board   | _   | 5.1   |                   | S       |

| Long Term Stability        |                  | <sup>O</sup>      |     | ≤0.01 | _                 | °C/Yr   |

Notes:

1. 14b measurement resolution (default). Values apply to the full operating temperature and voltage range of the device.

**2.** ±0.1 °C: +35.8 °C to 41 °C; ±0.13 °C: 20.0 °C to 70.0 °C; ±0.25 °C: –40 °C to +125 °C.

3. Time to reach 63% of final value in response to a step change in temperature. Actual response time will vary dependent on system thermal mass and air-flow.

#### Table 5. Thermal Characteristics

| Í | Parameter                            | Symbol        | Test Condition                          | DFN-6 | Unit |

|---|--------------------------------------|---------------|-----------------------------------------|-------|------|

|   | Junction to Air Thermal Resistance   | $\theta_{JA}$ | JEDEC 2-Layer board,<br>No Airflow      | 256   | °C/W |

|   | Junction to Air Thermal Resistance   | $\theta_{JA}$ | JEDEC 2-Layer board,<br>1 m/s Airflow   | 224   | °C/W |

|   | Junction to Air Thermal Resistance   | $\theta_{JA}$ | JEDEC 2-Layer board,<br>2.5 m/s Airflow | 205   | °C/W |

|   | Junction to Case Thermal Resistance  | $\theta_{JC}$ | JEDEC 2-Layer board                     | 22    | °C/W |

|   | Junction to Board Thermal Resistance | $\theta_{JB}$ | JEDEC 2-Layer board                     | 134   | °C/W |

### Table 6. Absolute Maximum Ratings<sup>1</sup>

| Parameter                             | Symbol | Test Condition | Min  | Тур | Max       | Unit |

|---------------------------------------|--------|----------------|------|-----|-----------|------|

| Ambient temperature<br>under bias     | 12     |                | -55  | _   | 125       | °C   |

| Storage Temperature <sup>2</sup>      | C      | 5              | -65  | _   | 150       | °C   |

| Voltage on I/O pins                   |        |                | -0.3 |     | VDD+0.3 V | V    |

| Voltage on VDD with<br>respect to GND |        | 0              | -0.3 |     | 4.2       | V    |

| ESD Tolerance                         |        | HBM            | _    |     | 2         | kV   |

|                                       |        | CDM            | _    |     | 1.25      | kV   |

|                                       |        | ММ             | _    | —   | 250       | V    |

#### Notes:

**1.** Absolute maximum ratings are stress ratings only, operation at or beyond these conditions is not implied and may shorten the life of the device or alter its performance.

2. Special handling considerations apply; see application note, "AN607: Si70xx Humidity and Temperature Sensor Designer's Guide".

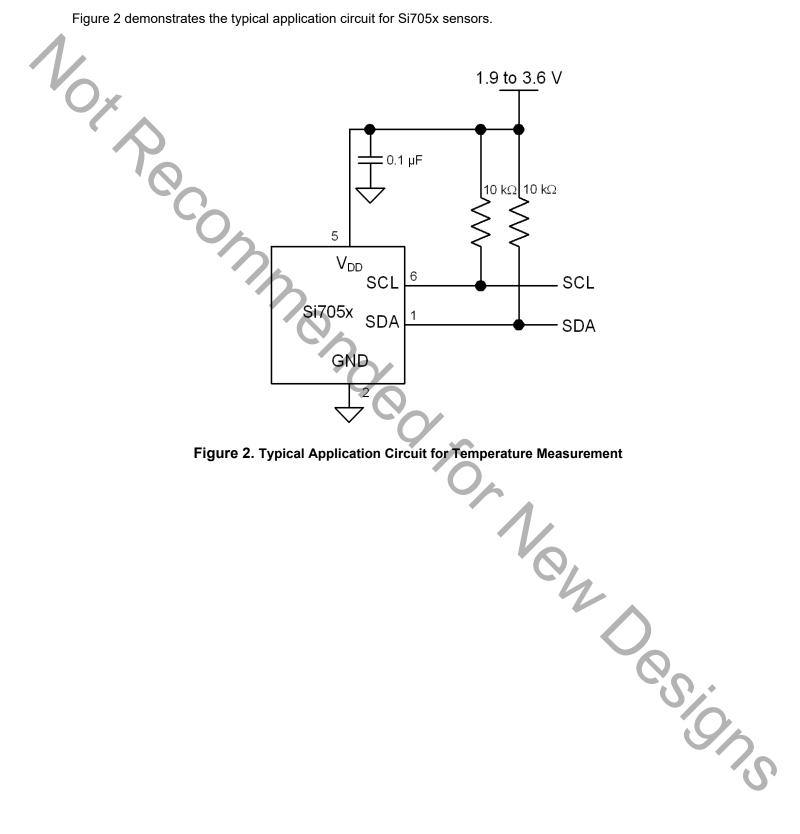

### 2. Typical Application Circuits

Figure 2 demonstrates the typical application circuit for Si705x sensors.

Figure 2. Typical Application Circuit for Temperature Measurement

### 3. Bill of Materials

| Reference |

|-----------|

| R1        |

| R2        |

| C1        |

| U1        |

|           |

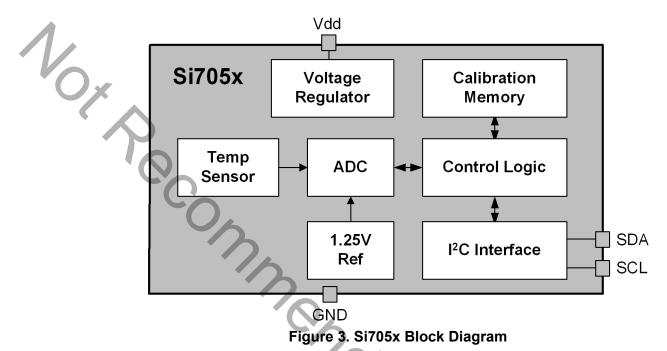

### 4. Functional Description

The Si705x Digital Temperature Sensors offer industry-leading low power consumption and high accuracy across the entire operating voltage and temperature range. These monolithic CMOS ICs feature a band-gap temperature sensor element, an analog-to-digital converter with up to 14-bit resolution, signal processing, calibration data, and an I<sup>2</sup>C interface. The patented use of novel signal processing and analog design enables the sensors to maintain their accuracy over a wide temperature and voltage range, while consuming very little current.

The temperature sensors are factory-calibrated and the calibration data is stored in the on-chip non-volatile memory. This ensures that the sensors are fully interchangeable, with no recalibration or software changes required.

The Si705x devices are available in a 3x3 mm DFN package, and the industry-standard I<sup>2</sup>C interface can operate at up to 400 kHz. Requiring just 195nA of average current when sampled once per second, the Si705x can operate for several years with just a single coin cell battery.

The Si705x devices offer an accurate, low-power, factory-calibrated digital solution ideal for measuring temperature in applications ranging from HVAC/R and asset tracking to industrial and consumer platforms.

Corions

## 5. I<sup>2</sup>C Interface

The Si705x communicates with the host controller over a digital  $I^2C$  interface. The 7-bit base slave address is 0x40 or 0x70 depending on the OPN (see "8. Ordering Guide" on page 19). When sending commands to the device, the R/W bit is set high for a read command and low for a write command.

| Ox | Table 8. I <sup>2</sup> C Slave Address Byte |    |    |    |    |    |     |  |

|----|----------------------------------------------|----|----|----|----|----|-----|--|

| A6 | A5                                           | A4 | A3 | A2 | A1 | A0 | R/W |  |

| 1  | 0                                            | 0  | 0  | 0  | 0  | 0  | 0   |  |

Master I<sup>2</sup>C devices communicate with the Si705x using a command structure. The commands are listed in the I<sup>2</sup>C command table. Commands other than those documented below are undefined and should not be sent to the device. When sending commands to the device, the R/W bit is set high for a read command and low for a write command.

| Command Description                      | Command Code |

|------------------------------------------|--------------|

| Measure Temperature, Hold Master Mode    | 0xE3         |

| Measure Temperature, No Hold Master Mode | 0xF3         |

| Reset                                    | 0xFE         |

| Write User Register 1                    | 0xE6         |

| Read User Register 1                     | 0xE7         |

| Read Electronic ID 1st Byte              | 0xFA 0x0F    |

| Read Electronic ID 2nd Byte              | 0xFC 0xC9    |

| Read Firmware Revision                   | 0x84 0xB8    |

|                                          | n O<br>Sio   |

### Table 9. I<sup>2</sup>C Command Table

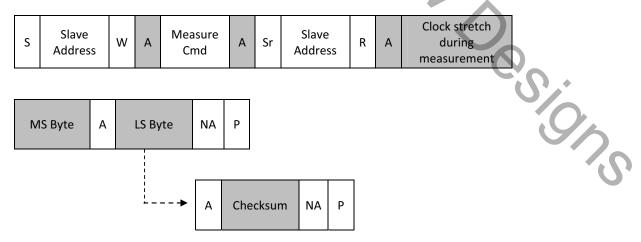

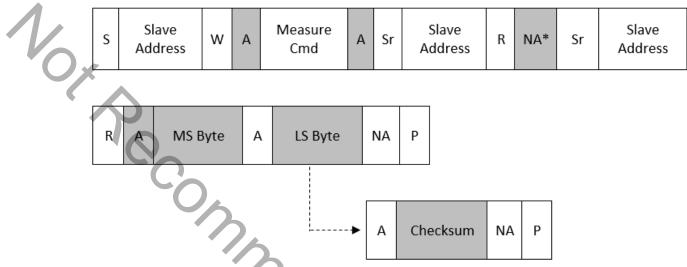

#### 5.1. Issuing a Measurement Command

The measurement command instructs the Si705x to perform a temperature measurement. While the measurement is in progress, the option of either clock stretching (Hold Master Mode) or Not Acknowledging read requests (No Hold Master Mode) is available to indicate to the master that the measurement is in progress; the chosen command code determines which mode is used.

Optionally, a checksum byte can be returned from the slave for use in checking for transmission errors. The checksum byte will follow the least significant measurement byte if it is acknowledged by the master. The checksum byte is not returned if the master "not acknowledges" the least significant measurement byte. The checksum byte is calculated using a CRC generator polynomial of  $x^8 + x^5 + x^4 + 1$ , with an initialization of 0x00.

The checksum byte is optional after initiating a temperature measurement with commands 0xE3, and 0xF3. The checksum byte is required for reading the electronic ID with commands 0xFA 0x0F and 0xFC 0xC9. For all other commands, the checksum byte is not supported.

| Name           | Symbol | Description                                                                                                                                                                                  |

|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START          | S      | SDA goes low while SCL high                                                                                                                                                                  |

| STOP           | Р      | SDA goes high while SCL high                                                                                                                                                                 |

| Repeated START | Sr     | SDA goes low while SCL high. It is allowable to generate a STOP before the repeated start. SDA can transition to high before or after SCL goes high in preparation for generating the START. |

| READ           | R      | Read bit = 0                                                                                                                                                                                 |

| WRITE          | W      | Write bit = 1                                                                                                                                                                                |

| All other bits | _      | SDA value must remain high or low during the entire time SCL is high (this is the set up and hold time in Figure 1)                                                                          |

#### Table 10. I<sup>2</sup>C Bit Descriptions

In the I<sup>2</sup>C sequence diagrams in the following sections, bits produced by the master and slave are color coded as shown:

Master Slave

#### Sequence to perform a measurement and read back result (Hold Master Mode)

#### Sequence to perform a measurement and read back result (No Hold Master Mode)

\*Note: Device will NACK the slave address byte until conversion is complete.

#### 5.1.1. Measuring Temperature

The measure temperature commands 0xE3 and 0xF3 will perform a temperature measurement and return the measurement value.

The results of the temperature measurement may be converted to temperature in degrees Celsius (°C) using the following expression:

Temperature (°C) =

$$\frac{175.72*Temp_Code}{65536} - 46.85$$

Where:

Temperature (°C) is the measured temperature value in °C

Temp\_Code is the 16-bit word returned by the Si705x

A temperature measurement will always return XXXXXX00 in the LSB field.

#### 5.2. Reading and Writing User Registers

There is one user register on the Si705x that allows the user to set the configuration of the Si705x. The procedure for accessing that register is described below.

The checksum byte is not supported after reading a user register.

|   | Sequence to read a register |   |   |                 |   |    |                  |   |   |           |      |

|---|-----------------------------|---|---|-----------------|---|----|------------------|---|---|-----------|------|

| S | Slave<br>Address            | W | А | Read Reg<br>Cmd | А | Sr | Slave<br>Address | R | А | Read Data | NA P |

#### Sequence to write a register

| _ |   |               |   |   | •             | - |            |   |   |

|---|---|---------------|---|---|---------------|---|------------|---|---|

|   | S | Slave Address | w | А | Write Reg Cmd | А | Write Data | А | Р |

### 5.3. Electronic Serial Number

The Si705x provides a serial number individualized for each device that can be read via the I<sup>2</sup>C serial interface.

Two I<sup>2</sup>C commands are required to access the device memory and retrieve the complete serial number. The command sequence, and format of the serial number response is described in the figure below:

| First acce | SS: |               |     | Maste | r SI | ave   |      |     |      |   |

|------------|-----|---------------|-----|-------|------|-------|------|-----|------|---|

|            | S   | Slave Address | W   | АСК   | 0xFA | АСК   | 0X0F | ACK |      |   |

|            | S   | Slave Address | R   | АСК   |      |       |      |     |      |   |

|            |     | SNA_3         | АСК | CRC   | ACK  | SNA_2 | ACK  | CRC | АСК  |   |

|            |     | SNA_1         | АСК | CRC   | ACK  | SNA_0 | ACK  | CRC | NACK | Р |

| 2nd acce   | SS: |               |     |       |      |       |      |     | 1    |   |

|            | S   | Slave Address | W   | ACK   | 0xFC | ACK   | 0XC9 | ACK |      |   |

|            | S   | Slave Address | R   | АСК   |      |       |      |     |      |   |

|            |     | SNB_3         | АСК | SNB_2 | ACK  | CRC   | ACK  |     |      |   |

|            |     | SNB_1         | АСК | SNB_0 | ACK  | CRC   | NACK | Р   |      |   |

The format of the complete serial number is 64-bits in length, divided into 8 data bytes. The complete serial number sequence is shown below:

| SNA_3 SNA_2 SNA_1 SNA_0 | SNB_3 | SNB_2 | SNB_1 | SNB_0 |

|-------------------------|-------|-------|-------|-------|

|-------------------------|-------|-------|-------|-------|

a dı. The SNB3 field contains the device identification to distinguish between the different Silicon Labs devices. The value of this field maps to the following devices according to this table:

0x00 or 0xFF engineering samples

50 = 0x32 = Si7050

- 51 = 0x33 = Si7051

- 53 = 0x35 = Si7053

- 54 = 0x36 = Si7054

- 55 = 0x37 = Si7055

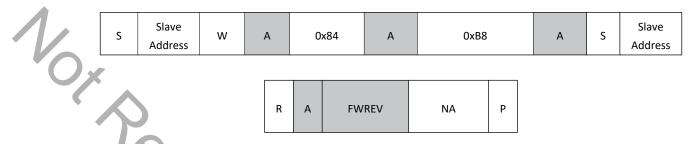

### 5.4. Firmware Revision

The internal firmware revision can be read with the following I<sup>2</sup>C transaction:

The values in this field are encoded as follows: sommended for New Designs

0xFF = Firmware version 1.0

0x20 = Firmware version 2.0.

### 6. Control Registers

| Register        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| User Register 1 | RES1  | VDDS  | RSVD  | RSVD  | RSVD  | RSVD  | RSVD  | RES0  |

| Notes:          |       |       |       |       |       |       |       |       |

#### Table 11. Register Summary

1. Any register not listed here is reserved and must not be written. The result of a read operation on these bits is undefined.

2. Except where noted, reserved register bits will always read back as "1," and are not affected by write operations. For future compatibility, it is recommended that prior to a write operation, registers should be read. Then the values read from the RSVD bits should be written back unchanged during the write operation.

### 6.1. Register Descriptions

| Register 1. User Register 1 | Register | 1. L | Jser | Register | 1 |  |

|-----------------------------|----------|------|------|----------|---|--|

|-----------------------------|----------|------|------|----------|---|--|

|      | -    |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|------|

| Bit  | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| Name | RES1 | VDDS | RSVD | RSVD | RSVD | RSVD | RSVD | RES0 |

| Туре | R/W  | R    | R/W  | R/   | W    | R/W  | R/W  | R/W  |

Reset Settings = 0011\_1010

| Bit                   | Name     | Function                                                                                                                                                                                                                                                                                                                  |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7; D0                | RES[1:0] | Measurement Resolution:           00:         14 bit           01:         12 bit           10:         13 bit           11:         11 bit                                                                                                                                                                               |

| D6                    | VDDS     | VDD Status:         0:       V <sub>DD</sub> OK         1:       V <sub>DD</sub> Low         The minimum recommended operating voltage is 1.9 V. A transition of the VDD status bit from 0 to 1 indicates that VDD is between 1.8 V and 1.9 V. If the VDD drops below 1.8 V, the device will no longer operate correctly. |

| D5, D4, D3,<br>D2, D1 | RSVD     | Reserved                                                                                                                                                                                                                                                                                                                  |

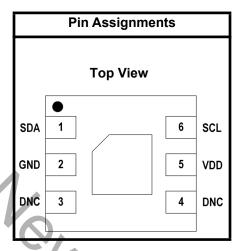

### 7. Pin Descriptions: Si705x (Top View)

|                                                                                                                                                                                             | 5     | GND 2 5 VDD                                                                                                                                      |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                                                             | 00    | DNC 3 4 DNC                                                                                                                                      |  |  |  |  |  |

| Pin Name                                                                                                                                                                                    | Pin # | Pin Description                                                                                                                                  |  |  |  |  |  |

| SDA                                                                                                                                                                                         | 1     | I <sup>2</sup> C data                                                                                                                            |  |  |  |  |  |

| GND                                                                                                                                                                                         | 2     | Ground. This pin is connected to ground on the circuit board through a trace. Do not connect directly to GND plane.                              |  |  |  |  |  |

| VDD                                                                                                                                                                                         | 5     | Power. This pin is connected to power on the circuit board.                                                                                      |  |  |  |  |  |

| SCL                                                                                                                                                                                         | 6     | I <sup>2</sup> C clock                                                                                                                           |  |  |  |  |  |

| DNC                                                                                                                                                                                         | 3,4   | These pins should be soldered to pads on the PCB for mechanical stability; they can be electrically floating or tied to VDD (do not tie to GND). |  |  |  |  |  |

| T <sub>GND</sub> Paddle This pad is connected to GND internally. This pad is the main thermal input to the on-<br>chip temperature sensor. The paddle should be soldered to a floating pad. |       |                                                                                                                                                  |  |  |  |  |  |

|                                                                                                                                                                                             |       |                                                                                                                                                  |  |  |  |  |  |

|                                                                                                                                                                                             |       |                                                                                                                                                  |  |  |  |  |  |

### 8. Ordering Guide

| Part Number                 | Description                | Max. Accuracy | Pkg   | Packing Format |

|-----------------------------|----------------------------|---------------|-------|----------------|

| Si7050-A20-IM               | Digital temperature sensor | ±1 °C         | DFN 6 | Cut Tape       |

| Si7050-A20-IMR              | Digital temperature sensor | ±1 °C         | DFN 6 | Tape and Reel  |

| Si7051-A20-IM <sup>2</sup>  | Digital temperature sensor | ±0.1 °C       | DFN 6 | Cut Tape       |

| Si7051-A20-IMR <sup>2</sup> | Digital temperature sensor | ±0.1 °C       | DFN 6 | Tape and Reel  |

| Si7053-A20-IM               | Digital temperature sensor | ±0.3 °C       | DFN 6 | Cut Tape       |

| Si7053-A20-IMR              | Digital temperature sensor | ±0.3 °C       | DFN 6 | Tape and Reel  |

| Si7054-A20-IM               | Digital temperature sensor | ±0.4 °C       | DFN 6 | Cut Tape       |

| Si7054-A20-IMR              | Digital temperature sensor | ±0.4 °C       | DFN 6 | Tape and Reel  |

| Si7055-A20-IM               | Digital temperature sensor | ±0.5 °C       | DFN 6 | Cut Tape       |

| Si7055-A20-IMR              | Digital temperature sensor | ±0.5 °C       | DFN 6 | Tape and Reel  |

| Si7055-A21-IM               | Digital temperature sensor | ±0.5 °C       | DFN 6 | Cut Tape       |

| Si7055-A21-IMR              | Digital temperature sensor | ±0.5 °C       | DFN 6 | Tape and Reel  |

### Table 12. Device Ordering Guide<sup>1</sup>

Notes:

1. The "A" denotes product revision A and "20" denotes firmware version 2.0. Part Numbers with -A21 denotes an I2C address of 0x70.

2. End of life.

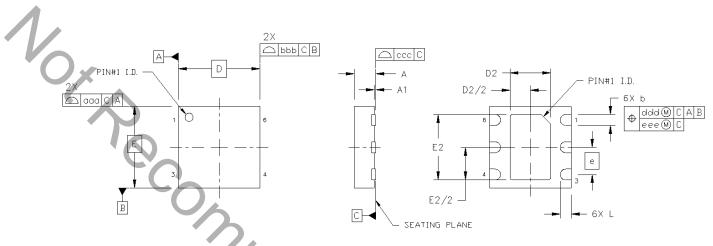

### 9. Package Outline

### 9.1. Package Outline: 3x3 6-Pin DFN

Figure 10. 3x3 6-pin DFN

|           | T denage Di                            |           |      |

|-----------|----------------------------------------|-----------|------|

| Dimension | Min                                    | Nom       | Max  |

| А         | 0.70                                   | 0.75      | 0.80 |

| A1        | 0.00                                   | 0.02      | 0.05 |

| b         | 0.35                                   | 0.40      | 0.45 |

| D         | 4                                      | 3.00 BSC. |      |

| D2        | 1.40                                   | 1.50      | 1.60 |

| е         |                                        | 1.00 BSC. |      |

| E         |                                        | 3.00 BSC. | 1    |

| E2        | 2.30                                   | 2.40      | 2.50 |

| L         | 0.35                                   | 0.40      | 0.45 |

| aaa       |                                        | 0.10      |      |

| bbb       |                                        | 0.10      |      |

| CCC       |                                        | 0.05      |      |

| ddd       |                                        | 0.10      |      |

| eee       |                                        | 0.05      |      |

|           | sions shown are i<br>ning and Tolerand |           |      |

#### Table 13. Package Diagram Dimensions

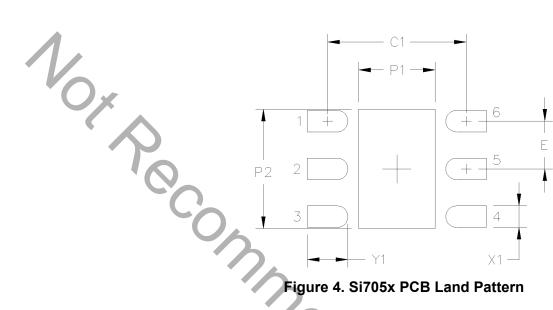

### 10. PCB Land Pattern and Solder Mask Design

Figure 4. Si705x PCB Land Pattern

#### **Table 14. PCB Land Pattern Dimensions**

| mm   |

|------|

| 2.90 |

| 1.00 |

| 1.60 |

| 2.50 |

| 0.45 |

| 0.85 |

|      |

### Notes:

#### General

- 1. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

#### Stencil Design

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- 7. A 2x1 array of 1.00 mm square openings on 1.30 mm pitch should be used for the center ground pad to achieve a target solder coverage of 50%.

#### **Card Assembly**

8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

50.0

### 11. Top Marking

### 11.1. Si705x Top Marking

### 11.2. Top Marking Explanation

#### 11.3. Si7055-A20-ZM (Matte Tin Finish Lead Frame) Top Marking

### 11.4. Si7055-A20-ZM (Matte Tin Finish Lead Frame) Top Marking Explanation

| Mark Method:LaserPin 1 Mark:Circle = 0.30 mm Diameter (Upper-<br>Left Corner)Font Size:0.05 mmLine 1 Mark Format:Device CodeSi7055Line 2 Mark Format:TTTTManufacturing Code from the<br>Assembly Purchase Order form.Line 3 Mark Format:YY = Year<br>WW = Work WeekWW = Work WeekAssigned by the Assembly House.<br>Corresponds to the year and work<br>week of the assembly release. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Left Corner)Font Size:0.05 mmLine 1 Mark Format:Device CodeSi7055Line 2 Mark Format:TTTTManufacturing Code from the<br>Assembly Purchase Order form.Line 3 Mark Format:YY = Year<br>WW = Work WeekAssigned by the Assembly House.<br>Corresponds to the year and work                                                                                                                 |

| Line 1 Mark Format:       Device Code       Si7055         Line 2 Mark Format:       TTTT       Manufacturing Code from the Assembly Purchase Order form.         Line 3 Mark Format:       YY = Year Work Week       Assigned by the Assembly House. Corresponds to the year and work                                                                                                |

| Line 2 Mark Format:       TTT       Manufacturing Code from the Assembly Purchase Order form.         Line 3 Mark Format:       YY = Year       Assigned by the Assembly House.         WW = Work Week       Corresponds to the year and work                                                                                                                                         |

| Line 3 Mark Format:       YY = Year       Assigned by the Assembly House.         WW = Work Week       Corresponds to the year and work                                                                                                                                                                                                                                               |

| WW = Work Week Corresponds to the year and work                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                       |

### 12. Additional Reference Resources

Nor Recommended for New Designs

### **DOCUMENT CHANGE LIST**

### **Revision 0.9 to Revision 1.0**

- Updated Section "5. I2C Interface" on page 12

- Updated Table 12, "Device Ordering Guide," on page 19

### Revision 1.0 to Revision 1.1

- Added part number Si7051

- Updated "9. Package Outline" on page 20

### Revision 1.1 to Revision 1.11

Added new OPN: Si7055-A20-ZM with matte tin finish lead frame

### Revision 1.11 to Revision 1.12

Removed erroneous typical value for Si7051 accuracy from Table 4.

### Revision 1.12 to Revision 1.13

Removed "YM0" and "YM0R" automotive qualified part numbers from Table 12, "Device Ordering Guide," on page 19.

#### **Revision 1.13 to Revision 1.14**

Updated "No Hold Master Mode" diagram in "5.1.

Issuing a Measurement Command" on page 13.

Updated diagram in "5.4. Firmware Revision" on page 16.'

■ Updated notes in Table 14, "PCB Land Pattern Dimensions," on page 21.

#### **Revision 1.14 to Revision 1.15**

■ Updated Table 12, "Device Ordering Guide," on page 19.

#### Revision 1.15 to Revision 1.2

■ Updated "8. Ordering Guide" on page 19 to include Si7055-A21-IM and Si7055-A21-IMR part numbers.

#### **Revision 1.2 to Revision 1.3**

Updated "8. Ordering Guide" on page 19 to note EOL parts.

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs product shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Lab

#### **Trademark Information**

Silicon Laboratories Inc.<sup>®</sup>, Silicon Laboratories<sup>®</sup>, Silicon Labs<sup>®</sup>, SiLabs<sup>®</sup> and the Silicon Labs logo<sup>®</sup>, Bluegiga<sup>®</sup>, Bluegiga Logo<sup>®</sup>, EFM<sup>®</sup>, EFM32<sup>®</sup>, EFR, Ember<sup>®</sup>, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Redpine Signals<sup>®</sup>, WiSeConnect, n-Link, ThreadArch<sup>®</sup>, EZRadio<sup>®</sup>, EZRadio<sup>®</sup>, EZRadio<sup>®</sup>, Gecko<sup>®</sup>, Gecko<sup>®</sup>, Gecko<sup>®</sup>, Gecko<sup>®</sup>, Gecko<sup>®</sup>, Gecko<sup>®</sup>, Gecko<sup>®</sup>, Studio<sup>®</sup>, Precision32<sup>®</sup>, Simplicity Studio<sup>®</sup>, Telegesis, the Telegesis Logo<sup>®</sup>, USBXpress<sup>®</sup>, Zentri, the Zentri logo and Zentri DMS, Z-Wave<sup>®</sup>, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

### www.silabs.com

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Silicon Laboratories:

<u>SI7053-A20-IMR</u> <u>SI7053-A20-IM</u> <u>SI7050-A20-IM</u> <u>SI7051-A20-IM</u> <u>SI7054-A20-IM</u> <u>SI7054-A20-IMR</u> <u>SI7055-A20-IMR</u> <u>SI7055-A20-IMR</u> <u>SI7055-A20-IMR</u> <u>SI7055-A20-IMR</u> <u>SI7055-A21-IMR</u>